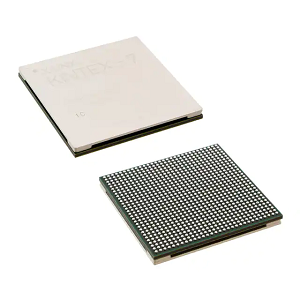

XC7K420T-2FFG901I – Sikui entegre, entegre, ranje pòtay pwogramasyon jaden

Atribi pwodwi

| TIP | ILUSTRE |

| kategori | Sikwi entegre (IC)Embedded Etalaj pòtay pwogramasyon jaden (FPGAs) |

| manifakti | AMD |

| seri | Kintex®-7 |

| vlope | plato |

| Estati pwodwi | Aktif |

| DigiKey se pwogramasyon | Pa verifye |

| Nimewo LAB/CLB | 32575 |

| Kantite eleman/inite lojik | 416960 |

| Kantite total Bits RAM | 30781440 |

| Kantite I/O | 380 |

| Voltage - Ekipman pou pouvwa | 0.97V ~ 1.03V |

| Kalite enstalasyon | Kalite adezif sifas |

| Tanperati opere | -40°C ~ 100°C (TJ) |

| Pake/Lojman | 900-BBGA、FCBGA |

| Encapsulation eleman vandè | 901-FCBGA (31x31) |

| Nimewo mèt pwodwi | XC7K420 |

| TIP | ILUSTRE |

| kategori | Sikwi entegre (IC)Embedded |

| manifakti | AMD |

| seri | Kintex®-7 |

| vlope | plato |

| Estati pwodwi | Aktif |

| DigiKey se pwogramasyon | Pa verifye |

| Nimewo LAB/CLB | 32575 |

| Kantite eleman/inite lojik | 416960 |

| Kantite total Bits RAM | 30781440 |

| Kantite I/O | 380 |

| Voltage - Ekipman pou pouvwa | 0.97V ~ 1.03V |

| Kalite enstalasyon | Kalite adezif sifas |

| Tanperati opere | -40°C ~ 100°C (TJ) |

| Pake/Lojman | 900-BBGA、FCBGA |

| Encapsulation eleman vandè | 901-FCBGA (31x31) |

| Nimewo mèt pwodwi | XC7K420 |

FPGA yo

Avantaj

Avantaj ki genyen nan FPGA yo se jan sa a:

(1) FPGA yo konpoze de resous pyès ki nan konpitè tankou selil lojik, RAM, miltiplikatè, elatriye Lè yo òganize resous pyès ki nan konpitè sa yo yon fason rasyonèl, yo ka aplike sikwi pyès ki nan konpitè tankou miltiplikatè, rejis, dèlko adrès, elatriye.

(2) FPGA yo ka fèt lè l sèvi avèk dyagram blòk oswa Verilog HDL, soti nan sikui pòtay senp nan sikui FIR oswa FFT.

(3) FPGA yo ka repwograme enfiniman, chaje yon nouvo solisyon konsepsyon nan jis kèk santèn milisgond, lè l sèvi avèk reconfiguration pou diminye sou tèt pyès ki nan konpitè.

(4) Frekans fonksyònman FPGA la detèmine pa chip FPGA ak konsepsyon an, epi yo ka modifye oswa ranplase ak yon chip pi rapid pou satisfè sèten kondisyon egzijan (byenke, nan kou, frekans fonksyònman an pa san limit epi li ka ogmante, men li gouvène pa pwosesis aktyèl IC ak lòt faktè).

Dezavantaj

Dezavantaj yo nan FPGA yo se jan sa a:

(1) FPGA yo konte sou aplikasyon pyès ki nan konpitè pou tout fonksyon epi yo pa kapab aplike operasyon tankou branch kondisyonèl so.

(2) FPGA yo ka aplike sèlman operasyon pwen fiks yo.

An rezime: FPGA yo konte sou pyès ki nan konpitè pou aplike tout fonksyon epi yo ka konpare ak bato devwe an tèm de vitès, men gen yon gwo diferans nan fleksibilite konsepsyon konpare ak processeurs bi jeneral.

Lang konsepsyon ak platfòm

Aparèy lojik pwogramab yo se transpòtè pyès ki nan konpitè ki konkretize fonksyon yo etabli ak espesifikasyon teknik aplikasyon elektwonik atravè teknoloji EDA.FPGA yo, kòm youn nan aparèy endikap ki aplike chemen sa a, yo dirèkteman oryante itilizatè yo, trè fleksib ak versatile, fasil pou itilize, epi rapid pou teste ak aplike nan pyès ki nan konpitè.

Lang deskripsyon pyès ki nan konpitè (HDL) se yon lang ki itilize pou konsepsyon sistèm lojik dijital ak dekri sikui dijital, prensipal yo ki souvan itilize yo se VHDL, Verilog HDL, System Verilog ak System C.

Kòm yon langaj deskripsyon pyès ki nan konpitè tout-wonn, trè wo vitès entegre sikwi deskripsyon pyès ki nan konpitè Lang (VHDL) gen karakteristik yo pou yo te endepandan de sikwi pyès ki nan konpitè espesifik ak endepandan de platfòm konsepsyon an, ak avantaj ki genyen nan kapasite deskripsyon lajè, pa depann sou aparèy espesifik, ak kapasite nan dekri konsepsyon an nan lojik kontwòl konplèks nan yon kòd solid ak kout, elatriye Li sipòte pa anpil konpayi EDA e li te lajman itilize nan jaden an nan konsepsyon elektwonik.lajman itilize.

VHDL se yon lang wo nivo pou konsepsyon sikwi, epi konpare ak lòt lang deskripsyon pyès ki nan konpitè, li gen karakteristik yon lang senp, fleksibilite ak endepandans nan konsepsyon aparèy, fè li yon lang deskripsyon pyès ki nan konpitè komen pou teknoloji EDA ak fè teknoloji EDA plis. aksesib a konsèpteur yo.

Verilog HDL se yon langaj deskripsyon pyès ki nan konpitè lajman itilize ki ka itilize nan plizyè etap nan pwosesis konsepsyon pyès ki nan konpitè, ki gen ladan modèl, sentèz ak simulation.

Avantaj Verilog HDL: menm jan ak C, fasil pou aprann ak fleksib.Ka-sansib.Avantaj nan estimilis ekri ak modèl.Dezavantaj: anpil erè pa ka detekte nan tan konpile.

Avantaj VHDL: Sentaks rijid, yerachi klè.Dezavantaj: tan familyarize long, pa fleksib ase.

Lojisyèl Quartus_II se yon anviwònman konsepsyon milti-platfòm konplè devlope pa Altera, ki ka satisfè bezwen konsepsyon divès kalite FPGA ak CPLD, epi li se yon anviwònman konplè pou konsepsyon sistèm pwogramasyon sou chip.

Vivado Design Suite, yon anviwònman konsepsyon entegre ki te pibliye pa machann FPGA Xilinx an 2012. Li gen ladann yon anviwònman konsepsyon trè entegre ak yon nouvo jenerasyon zouti soti nan sistèm nan nivo IC, tout bati sou yon modèl done pataje évolutive ak yon anviwònman debug komen.Xilinx Vivado Design Suite la bay nwayo IP FIFO ki ka fasil aplike nan desen.