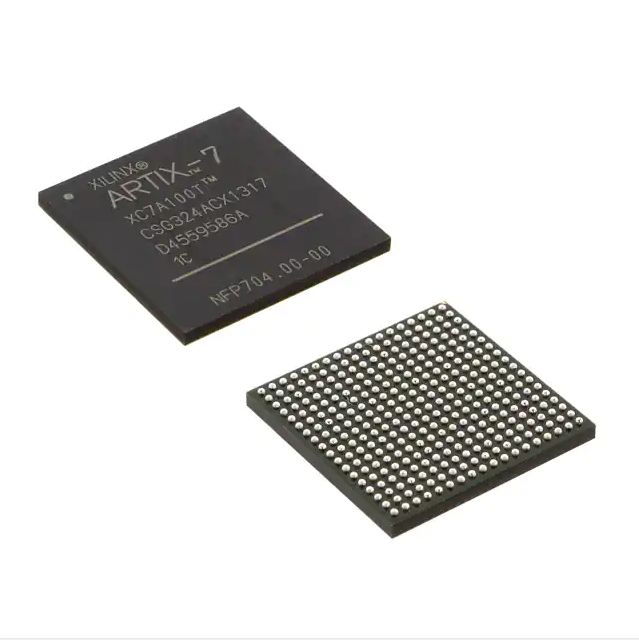

XC7A100T-2FGG676C – Sikui entegre, entegre, ranje pòtay pwogramasyon jaden

Atribi pwodwi

| TIP | ILUSTRE |

| kategori | Sikwi entegre (IC) |

| manifakti | AMD |

| seri | Artix-7 |

| vlope | plato |

| Estati pwodwi | Aktif |

| DigiKey se pwogramasyon | Pa verifye |

| Nimewo LAB/CLB | 7925 |

| Kantite eleman/inite lojik | 101440 |

| Kantite total Bits RAM | 4976640 |

| Kantite I/O | 300 |

| Voltage - Ekipman pou pouvwa | 0.95V ~ 1.05V |

| Kalite enstalasyon | Kalite adezif sifas |

| Tanperati opere | 0°C ~ 85°C (TJ) |

| Pake/Lojman | 676-BGA |

| Encapsulation eleman vandè | 676-FBGA (27x27) |

| Nimewo mèt pwodwi | XC7A100 |

Files & Media

| TIP RESOUS | LYEN |

| Fich done | Artix-7 FPGAs Datasheet |

| Inite fòmasyon pwodwi | Alimente Seri 7 Xilinx FPGAs ak TI Power Management Solutions |

| Enfòmasyon sou anviwònman an | Xiliinx RoHS Sèt |

| Pwodwi ki prezante yo | Artix®-7 FPGA |

| EDA modèl | XC7A100T-2FGG676C pa Ultra Bibliyotekè |

| Errata | XC7A100T/200T Errata |

Klasifikasyon nan espesifikasyon anviwònman ak ekspòtasyon

| ATRIBITE | ILUSTRE |

| estati RoHS | Konfòme ak direktiv ROHS3 |

| Nivo sansiblite imidite (MSL) | 3 (168 èdtan) |

| estati REACH | Pa sijè a spesifikasyon REACH |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Aplikasyon endistri pou FPGAs

Sistèm divize videyo

Nan dènye ane yo, gwo sistèm kontwòl total yo te de pli zan pli lajman itilize, ak nivo nan teknoloji segmentation videyo ki asosye ak yo tou piti piti amelyore, se teknoloji a mete ak yon ekspozisyon asanblaj milti-ekran yo montre yon siyal videyo tout wout la, nan kèk bezwen sèvi ak yon gwo ekran ekspozisyon senaryo lajman itilize.

Avèk avansman teknoloji, teknoloji segmentasyon videyo piti piti matirite pou satisfè bezwen debaz moun pou imaj videyo klè, estrikti pyès ki nan konpitè chip FPGA se relativman espesyal, ou ka itilize dosye estrikti lojik ki te fèt avan modifye pou ajiste estrikti entèn la, itilizasyon an. nan dosye contrainte ajiste koneksyon an ak kote nan inite lojik diferan, manyen apwopriye nan chemen an liy done, fleksibilite pwòp li yo ak adaptabilite fasilite itilizatè a fleksibilite pwòp li yo ak adaptabilite fasilite devlopman itilizatè ak aplikasyon.Lè w ap trete siyal videyo yo, chip FPGA a ka pran anpil avantaj de vitès ak estrikti li pou aplike teknik ping-pong ak tiyo.Nan pwosesis koneksyon ekstèn, chip la sèvi ak done koneksyon paralèl pou elaji lajè ti jan nan enfòmasyon imaj la epi sèvi ak fonksyon lojik entèn yo pou ogmante vitès pwosesis imaj la.Kontwòl pwosesis imaj ak lòt aparèy reyalize atravè estrikti kachèt ak jesyon revèy.Chip FPGA a se nan kè estrikti konsepsyon an jeneral, entèpolasyon done konplèks kòm byen ke ekstrè ak estoke li, epi tou li jwe yon wòl nan kontwòl jeneral asire operasyon an ki estab nan sistèm nan.Anplis de sa, pwosesis enfòmasyon videyo diferan de lòt pwosesis done epi li mande pou chip la gen inite lojik espesyal ak inite RAM oswa FIFO pou asire ke vitès transmisyon done ase ogmante.

Reta done ak konsepsyon depo

FPGA yo gen inite dijital reta pwogramasyon epi yo gen yon pakèt aplikasyon nan sistèm kominikasyon ak divès kalite aparèy elektwonik, tankou sistèm kominikasyon synchrone, sistèm nimerik tan, elatriye. Metòd konsepsyon prensipal yo enkli metòd liy reta CNC, metòd memwa, kontwa an. metòd, elatriye, kote metòd memwa a sitou aplike lè l sèvi avèk RAM oswa FIFO FPGA a.

Itilizasyon FPGA yo pou li ak ekri done ki gen rapò ak kat SD ka baze sou bezwen algorithm espesifik nan chip FPGA ki ba pou pote pwogramasyon, chanjman ki pi reyalis pou reyalize operasyon lekti ak ekri toujou ap mete ajou.Mòd sa a sèlman mande pou itilize chip ki deja egziste a pou reyalize kontwòl efikas kat SD la, siyifikativman diminye pri sistèm lan.

Endistri kominikasyon

Anjeneral, endistri kominikasyon an, pran an kont tout faktè tankou pri ak operasyon, gen plis chans pou yo sèvi ak FPGA nan kote ki kantite aparèy tèminal yo wo.Estasyon debaz yo pi apwopriye pou itilize FPGA, kote prèske chak tablo bezwen sèvi ak yon chip FPGA, ak modèl yo relativman wo-fen epi yo ka okipe pwotokòl fizik konplèks ak reyalize kontwòl lojik.An menm tan an, kòm kouch lyen ki lojik estasyon baz la, pati nan pwotokòl nan kouch fizik la bezwen mete ajou regilyèman, ki se tou pi apwopriye pou teknoloji FPGA.Kounye a, FPGA yo sitou itilize nan premye etap yo byen bonè ak nan mitan konstriksyon nan endistri kominikasyon, epi yo piti piti ranplase pa ASIC nan yon etap pita.

Lòt aplikasyon

FPGA yo tou lajman itilize nan aplikasyon pou sekirite ak endistriyèl, pou egzanp, kodaj videyo ak pwotokòl dekodaj nan jaden sekirite a ka trete lè l sèvi avèk FPGA nan pwosesis pou akizisyon done devan ak kontwòl lojik.Pi piti echèl FPGA yo itilize nan sektè endistriyèl la pou satisfè bezwen fleksibilite.Anplis de sa, FPGA yo tou lajman itilize nan militè a kòm byen ke nan sektè ayewospasyal la akòz fyab relativman wo yo.Nan lavni an, ak amelyorasyon kontinyèl nan teknoloji, pwosesis ki enpòtan yo pral modènize, ak FPGA yo pral gen yon pwospè aplikasyon pi laj nan anpil nouvo endistri tankou gwo done.Avèk konstriksyon rezo 5G, FPGA yo pral itilize an gwo kantite nan premye etap yo, ak nouvo jaden tankou entèlijans atifisyèl pral wè tou plis itilizasyon FPGA.

Nan mwa fevriye 2021, FPGA yo, ki ka achte ak Lè sa a, fèt, yo te rele "chips inivèsèl".Konpayi an, youn nan pi bonè konpayi domestik yo pou devlope poukont yo, pwodwi an mas ak vann chips FPGA jeneral, te finalize yon envestisman 300 milyon dola Yuan nan yon nouvo jenerasyon domestik FPGA chip R&D ak pwojè endistriyalizasyon nan Yizhuang.