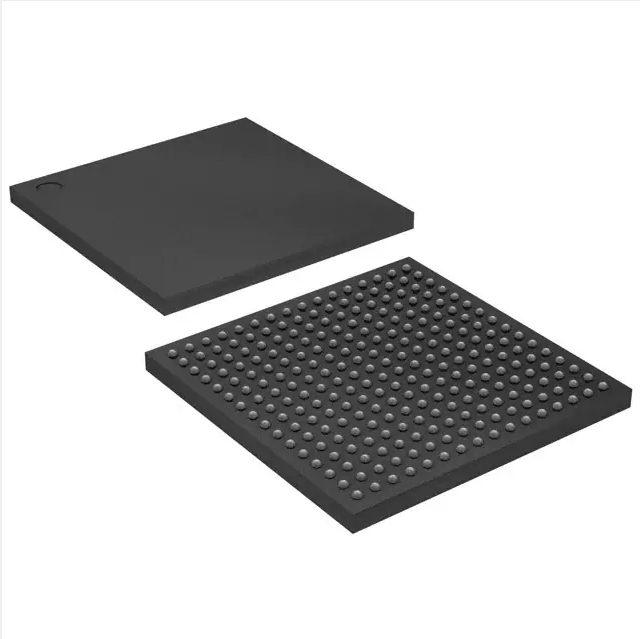

XCZU19EG-2FFVC1760E 100% nouvo & orijinal DC a DC konvètisè & chanje Chip regilatè

Atribi pwodwi

| Atribi pwodwi | Valè atribi |

| Manifakti: | Xilinx |

| Kategori pwodwi: | SoC FPGA |

| Restriksyon sou livrezon: | Pwodui sa a ka mande lòt dokiman pou ekspòte soti nan Etazini. |

| RoHS: | Detay yo |

| Style monte: | SMD/SMT |

| Pake / Ka: | FBGA-1760 |

| Nwayo: | ARM Cortex A53, ARM Cortex R5, ARM Mali-400 MP2 |

| Kantite Nwayo: | 7 Nwayo |

| Frekans revèy maksimòm: | 600 MHz, 667 MHz, 1.5 GHz |

| L1 Cache Memwa Enstriksyon: | 2 x 32 kB, 4 x 32 kB |

| L1 Cache done memwa: | 2 x 32 kB, 4 x 32 kB |

| Gwosè memwa pwogram: | - |

| Done RAM Size: | - |

| Kantite eleman lojik: | 1143450 LE |

| Modil lojik adaptab - ALM: | 65340 ALM |

| Memwa entegre: | 34.6 Mbit |

| Fonksyone Voltage Pwovizyon pou: | 850 mV |

| Tanperati Minimòm Fonksyònman: | 0 C |

| Maksimòm Tanperati Fonksyònman: | + 100 C |

| Mak: | Xilinx |

| Distribiye RAM: | 9.8 Mbit |

| Blòk entegre RAM - EBR: | 34.6 Mbit |

| Sansib imidite: | Wi |

| Kantite blòk etalaj lojik - LAB: | 65340 LAB |

| Kantite transceiver: | 72 Transceiver |

| Kalite pwodwi: | SoC FPGA |

| Seri: | XCZU19EG |

| Kantite pake faktori: | 1 |

| Sou-kategori: | SOC la vle di Sistèm sou yon chip |

| Non komès: | Zynq UltraScale+ |

Kalite sikwi entegre

Konpare ak elektwon, foton pa gen okenn mas estatik, entèraksyon fèb, fò kapasite anti-entèferans, epi yo pi apwopriye pou transmisyon enfòmasyon.Interkoneksyon optik espere vin teknoloji debaz la kraze nan miray la konsomasyon pouvwa, miray depo ak miray kominikasyon.Limine, kouple, modulator, aparèy ond yo entegre nan karakteristik optik segondè dansite yo tankou sistèm fotoelektrik entegre mikwo, ka reyalize bon jan kalite, volim, konsomasyon pouvwa nan entegrasyon fotoelektrik segondè dansite, platfòm entegrasyon fotoelektrik ki gen ladan III - V konpoze semi-conducteurs monolitik entegre (INP). ) platfòm entegrasyon pasif, silikat oswa vè (planè optik waveguide, PLC) platfòm ak platfòm Silisyòm ki baze sou.

InP platfòm se sitou itilize pou pwodiksyon lazè, modulator, detektè ak lòt aparèy aktif, nivo teknoloji ki ba, pri segondè substra;Sèvi ak platfòm PLC pou pwodwi konpozan pasif, pèt ki ba, gwo volim;Pwoblèm nan pi gwo ak tou de platfòm se ke materyèl yo pa konpatib ak elektwonik ki baze sou Silisyòm.Avantaj ki pi enpòtan nan entegrasyon fotonik ki baze sou Silisyòm se ke pwosesis la konpatib ak pwosesis CMOS ak pri pwodiksyon an ba, kidonk li konsidere kòm konplo entegrasyon optoelectronic ki pi potansyèl ak menm tout-optik.

Gen de metòd entegrasyon pou aparèy fotonik ki baze sou Silisyòm ak sikui CMOS.

Avantaj nan ansyen an se ke aparèy fotonik yo ak aparèy elektwonik yo ka optimize separeman, men anbalaj ki vin apre a difisil ak aplikasyon komèsyal yo limite.Lèt la difisil pou konsepsyon ak pwosesis entegrasyon de aparèy yo.Kounye a, asanble ibrid ki baze sou entegrasyon patikil nikleyè se pi bon chwa