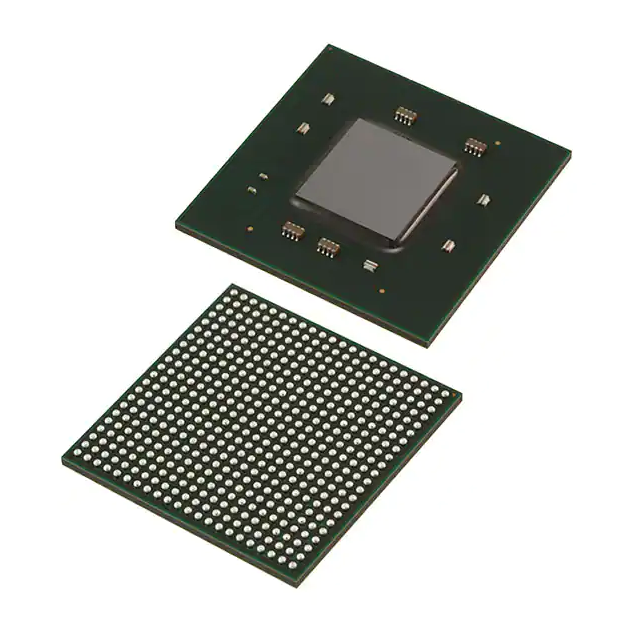

Nouvo ak orijinal XC7A100T-2FGG484I IC sikwi entegre FPGA jaden Programmable Gate Array ad8313 IC FPGA 285 I/O 484FBGA

Atribi pwodwi

| TIP | DESKRIPSYON |

| Kategori | Sikwi entegre (IC)Embedded |

| Mfr | AMD Xilinx |

| Seri | Artix-7 |

| Pake | Plato |

| Pake estanda | 60 |

| Estati pwodwi | Aktif |

| Kantite LAB/CLB | 7925 |

| Kantite Eleman Lojik/Selil | 101440 |

| Total Bits RAM | 4976640 |

| Kantite I/O | 285 |

| Voltage - Pwovizyon pou | 0.95V ~ 1.05V |

| Kalite aliye | Sifas mòn |

| Tanperati Fonksyònman | -40°C ~ 100°C (TJ) |

| Pake / Ka | 484-BBGA |

| Pake Aparèy Founisè | 484-FBGA (23×23) |

| Nimewo pwodwi de baz | XC7A100 |

Sèvi ak FPGA kòm processeur trafik pou sekirite rezo a

Trafik pou ale ak pou soti nan aparèy sekirite (pare-feu) yo ankripte nan plizyè nivo, epi L2 chifreman/dekripte (MACSec) trete nan kouch lyen (L2) nœuds rezo (switch ak routeurs).Pwosesis pi lwen pase L2 (kouch MAC) anjeneral gen ladan parsing pi fon, dechifre tinèl L3 (IPSec), ak trafik SSL chiffres ak trafik TCP/UDP.Pwosesis pake enplike nan analiz ak klasifikasyon nan pake fèk ap rantre ak pwosesis la nan komèsan trafik gwo (1-20M) ak gwo debi (25-400Gb / s).

Akòz gwo kantite resous enfòmatik (nwayo) ki nesesè yo, NPU yo ka itilize pou pwosesis pake vitès relativman pi wo, men latansi ki ba, pwosesis sikilasyon wo-pèfòmans pa posib paske trafik yo trete lè l sèvi avèk nwayo MIPS/RISC ak orè debaz sa yo. baze sou disponiblite yo difisil.Itilizasyon aparèy sekirite ki baze sou FPGA ka efektivman elimine limit sa yo nan CPU ak achitekti ki baze sou NPU.

Pwosesis sekirite nivo aplikasyon nan FPGA yo

FPGA yo ideyal pou pwosesis sekirite aliye nan pwochen jenerasyon firewall paske yo satisfè avèk siksè bezwen pou pi wo pèfòmans, fleksibilite ak operasyon ki ba-latansi.Anplis de sa, FPGA yo kapab aplike tou fonksyon sekirite nan nivo aplikasyon an, sa ki ka plis sove resous informatique ak amelyore pèfòmans.

Egzanp komen nan pwosesis sekirite aplikasyon nan FPGA yo enkli

- TTCP dechaje motè

- Matche ekspresyon regilye

- Asymetrik chifreman (PKI) pwosesis

- TLS pwosesis

Teknoloji sekirite pwochen jenerasyon lè l sèvi avèk FPGA

Anpil algoritm asimetri ki deja egziste yo vilnerab a konpwomi pa òdinatè pwopòsyon.Algoritm sekirite asimetrik tankou RSA-2K, RSA-4K, ECC-256, DH, ak ECCDH se teknik informatique pwopòsyon ki pi afekte yo.Nouvo aplikasyon algoritm asimetri ak normalisation NIST yo ap eksplore.

Pwopozisyon aktyèl pou chifreman pòs pwopòsyon yo enkli metòd aprantisaj Ring-on-Error (R-LWE) pou

- Kriptografi kle piblik (PKC)

- Siyati dijital

- Kreyasyon kle

Aplikasyon ki pwopoze nan kriptografi kle piblik la gen ladan sèten operasyon matematik byen li te ye (TRNG, echantiyon bri Gaussian, adisyon polinòm, divizyon quantifier binè polinòm, miltiplikasyon, elatriye).FPGA IP pou anpil nan algoritm sa yo disponib oswa yo ka aplike avèk efikasite lè l sèvi avèk blòk bilding FPGA, tankou DSP ak AI motè (AIE) nan aparèy Xilinx ki deja egziste ak pwochen jenerasyon.

Papye blan sa a dekri aplikasyon sekirite L2-L7 lè l sèvi avèk yon achitekti pwogramasyon ki ka deplwaye pou akselerasyon sekirite nan rezo kwen/aksè ak firewall pwochen jenerasyon (NGFW) nan rezo antrepriz.