LM46002AQPWPRQ1 pake HTSSOP16 sikwi entegre IC chip nouvo orijinal konpozan elektwonik plas

Atribi pwodwi

| TIP | DESKRIPSYON |

| Kategori | Sikwi entegre (IC) |

| Mfr | Texas Instruments |

| Seri | Otomobil, AEC-Q100, SIMPLE SWITCHER® |

| Pake | Tap & Bobine (TR) Koupe tep (CT) Digi-Reel® |

| SPQ | 2000T&R |

| Estati pwodwi | Aktif |

| Fonksyon | Desann |

| Konfigirasyon Sòti a | Pozitif |

| Topoloji | Buck |

| Kalite Sòti | Reglabl |

| Kantite Sòti yo | 1 |

| Voltage - Antre (Min) | 3.5V |

| Voltage - Antre (Max) | 60V |

| Voltage - Sòti (Min/Fiks) | 1V |

| Voltage - Sòti (Max) | 28V |

| Kouran - Sòti | 2A |

| Frekans - Chanje | 200kHz ~ 2.2MHz |

| Synchrone redresman | Wi |

| Tanperati Fonksyònman | -40°C ~ 125°C (TJ) |

| Kalite aliye | Sifas mòn |

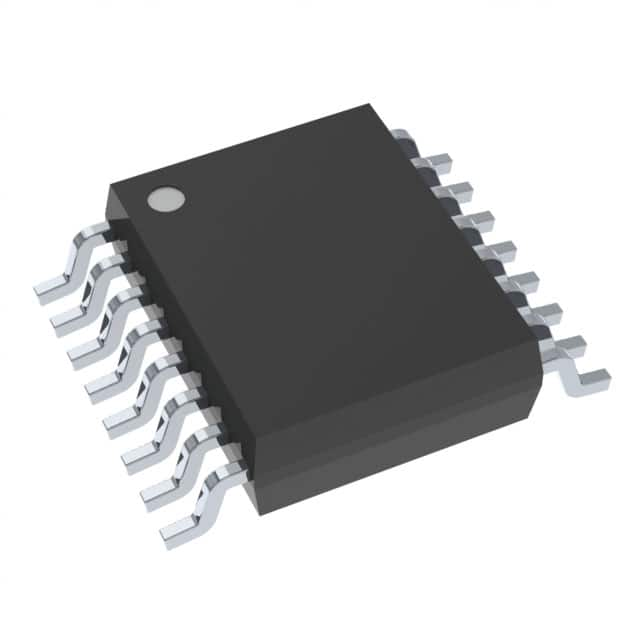

| Pake / Ka | 16-TSSOP (0.173", 4.40mm Lajè) Ekspoze Pad |

| Pake Aparèy Founisè | 16-HTSSOP |

| Nimewo pwodwi de baz | LM46002 |

Pwosesis pwodiksyon chip

Pwosesis fabrikasyon chip konplè a gen ladan konsepsyon chip, pwodiksyon wafer, anbalaj chip, ak tès chip, nan mitan ki pwosesis pwodiksyon wafer la patikilyèman konplèks.

Premye etap la se konsepsyon chip la, ki baze sou kondisyon konsepsyon yo, tankou objektif fonksyonèl, espesifikasyon, layout sikwi, likidasyon fil ak detaye, elatriye "desen konsepsyon" yo pwodwi;fotomask yo pwodui davans selon règ chip yo.

②.Pwodiksyon wafer.

1. Silisyòm gaufre yo koupe nan epesè ki nesesè yo lè l sèvi avèk yon tranche wafer.Pi mens wafer la, pi ba pri a nan pwodiksyon, men plis mande pwosesis la.

2. plak blanch sifas wafer ak yon fim photoresist, ki amelyore wafer rezistans pou D' ak tanperati.

3. Wafer fotolitografi devlopman ak grave itilize pwodwi chimik ki sansib a UV limyè, sa vle di yo vin douser lè ekspoze a UV limyè.Ou ka jwenn fòm chip la lè w kontwole pozisyon mask la.Yo aplike yon fotorezist sou wafer Silisyòm pou li fonn lè ekspoze a limyè UV.Sa a se fè lè w aplike premye pòsyon nan mask la pou ke pati a ki ekspoze a limyè UV fonn epi pati sa a ki fonn ka Lè sa a, dwe lave lwen ak yon sòlvan.Lè sa a, pati ki fonn sa a ka lave lwen ak yon sòlvan.Se pati ki rete a Lè sa a, ki gen fòm tankou photoresist la, ki ban nou kouch nan silica vle.

4. Piki iyon.Sèvi ak yon machin grave, pyèj N ak P yo grave nan Silisyòm fè a, ak iyon yo enjekte yo fòme yon junction PN (pòtay lojik);Lè sa a, kouch metal anwo a konekte ak kous la pa presipitasyon move tan chimik ak fizik.

5. Tès wafer Apre pwosesis ki anwo yo, yon lasi nan zo fòme sou wafer la.Yo teste karakteristik elektrik chak mouri lè l sèvi avèk tès PIN.

③.Anbalaj chip

Wafer la fini fiks, mare ak broch, epi li fè nan divès pakè selon demann.Egzanp: DIP, QFP, PLCC, QFN, ak sou sa.Sa a se sitou detèmine pa abitid aplikasyon itilizatè a, anviwònman aplikasyon an, sitiyasyon mache a, ak lòt faktè periferik.

④.Tès chip

Pwosesis final la nan fabrikasyon chip se tès pwodwi fini, ki ka divize an tès jeneral ak tès espesyal, ansyen an se teste karakteristik elektrik yo nan chip la apre anbalaj nan divès anviwònman, tankou konsomasyon pouvwa, vitès opere, rezistans vòltaj, elatriye Apre tès la, bato yo klase nan diferan klas selon karakteristik elektrik yo.Tès espesyal la baze sou paramèt teknik nan bezwen espesyal kliyan an, ak kèk chips ki soti nan espesifikasyon menm jan an ak varyete yo teste yo wè si yo ka satisfè bezwen espesyal kliyan an, deside si bato espesyal yo ta dwe fèt pou kliyan an.Pwodwi ki te pase tès jeneral yo make ak espesifikasyon, nimewo modèl, ak dat faktori yo epi yo pake anvan yo kite faktori a.Chips ki pa pase tès la klase kòm déklasé oswa rejte selon paramèt yo te reyalize.

.png)