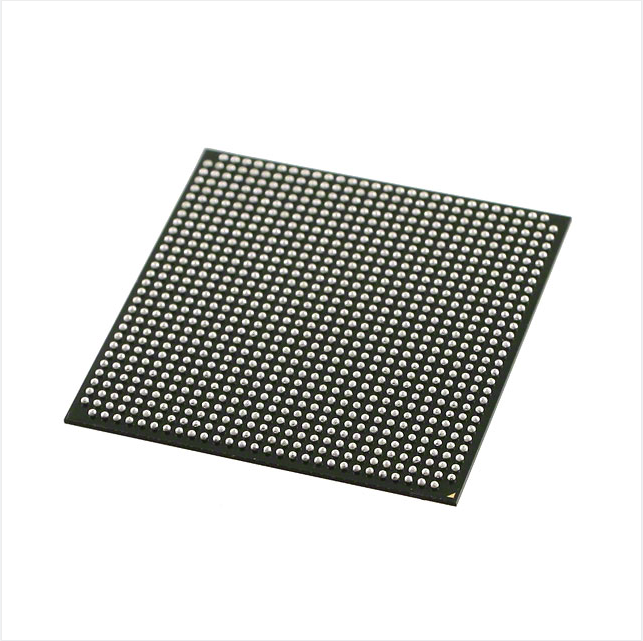

5CEFA7F31I7N nouvo & orijinal ic chips sikwi entegre konpozan elektwonik pi bon pri yon sèl plas achte sèvis BOM

Atribi pwodwi

| TIP | DESKRIPSYON |

| Kategori | Sikwi entegre (IC) |

| Mfr | Intel |

| Seri | Cyclone® VE |

| Pake | Plato |

| Pake estanda | 27 |

| Estati pwodwi | Aktif |

| Kantite LAB/CLB | 56480 |

| Kantite Eleman Lojik/Selil | 149500 |

| Total Bits RAM | 7880704 |

| Kantite I/O | 480 |

| Voltage - Pwovizyon pou | 1.07V ~ 1.13V |

| Kalite aliye | Sifas mòn |

| Tanperati Fonksyònman | -40°C ~ 100°C (TJ) |

| Pake / Ka | 896-BGA |

| Pake Aparèy Founisè | 896-FBGA (31×31) |

| Nimewo pwodwi de baz | 5CEFA7 |

1. Virtex seri FPGAs pou pèfòmans segondè

Seri Virtex la se pwodwi wo-fen Xilinx a ak pwodwi ki pi wo nan endistri an.Xilinx te genyen mache a ak pwodwi seri Virtex li yo, konsa pran pozisyon kòm dirijan founisè FPGA.Li ka di ke Xilinx mennen endistri etalaj pòtay jaden pwogramasyon ak fanmi Virtex li yo nan pwodwi FPGA.Li se sitou ki vize a aplikasyon tankou enfrastrikti telecom, endistri otomobil la, ak elektwonik konsomatè-wo fen.Chip endikap aktyèl yo gen ladan kategori Vitrex-2, Virtex-2 Pro, Virtex-4, Virtex-5, Virtex-6 ak Virtex-7.

Seri Virtex-2 te prezante an 2002 ak yon pwosesis 0.15nm, 1.5V vòltaj debaz, revèy opere jiska 420MHz, sipò pou plis pase 20 estanda koòdone I/O, kapasite konplè jesyon revèy sistèm, ak konstriksyon IP nwayo difisil. teknoloji debaz ki pèmèt nwayo IP difisil yo dwe asiyen nenpòt kote sou chip la, ak plis resous ak pi wo pèfòmans pase seri Virtex la.pèfòmans ki pi wo pase fanmi Virtex la.

Seri Virtex-2 Pro a bati sou Virtex-2 ak kapasite pwosesis entegre amelyore, ak nwayo PowerPC405 entegre, epi li gen ladan teknoloji avanse Interconnect Active pou adrese defi sistèm pèfòmans segondè yo fè fas a, anplis de yon gwo vitès. seri transceiver pou bay solisyon Gigabit Ethernet.

Fanmi Virtex-4 la baze sou achitekti Advanced Silicon Block Combination Module (ASMBL), ki gen gwo dansite lojik ak frekans revèy jiska 500 MHz;ak modil DCM, PMCD faz-matche revèy divize, rezo revèy diferans sou-chip;Teknoloji SmartRAM 500 MHz ak lojik kontwòl FIFO entegre, epi chak I/O entegre ak teknoloji senkronizasyon sous ChipSync pou 1 Gbps I/O ak chip lojik Xtreme DSP.Konsèpteur yo ka chwazi diferan sous-sistèm Virtex-4 selon bezwen yo, pou konsepsyon lojik entansif: Virtex-4 LX, pou aplikasyon pou pwosesis siyal pèfòmans segondè: Virtex-4 SX, pou koneksyon seri gwo vitès ak aplikasyon pou pwosesis entegre: Virtex- 4 FX.Fanmi Virtex-4 ofri yon amelyorasyon siyifikatif nan tout mezi sou VirtexII Seri Virtex-4 la, ki te nan pwodiksyon an mas depi nan fen 2005, te ranplase VirtexII, VirtexII-Pro, epi li se pwodwi ki pi enpòtan Xilinx a nan segondè jodi a. -fen mache FPGA.

Fanmi Virtex-5 la baze sou dènye teknoloji pwosesis kwiv 65nm e li sèvi ak yon achitekti kolòn ASMBL (Advanced Silicon Building Block) dezyèm jenerasyon, ki gen senk tribin diferan (soufami).Chak platfòm gen rapò karakteristik diferan pou satisfè bezwen anpil desen lojik avanse.Anplis de dènye achitekti lojik pèfòmans-wo, Virtex-5 FPGA yo gen ladan yon varyete modil nivo sistèm difisil-IP, ki gen ladan yon pwisan 36 Kb blòk RAM/FIFO, yon dezyèm jenerasyon 25×18. DSP Slice, SelectIO teknoloji ak enpedans CNC entegre, modil koòdone senkronizasyon sous ChipSync, fonksyonalite pou kontwole sistèm, ak yon dèlko revèy DCM (Digital Clock Manager) ak PLL (Phase Locked Loop) entegre, ak opsyon konfigirasyon avanse.Lòt karakteristik ki baze sou platfòm yo enkli yon modil transceiver seri gwo vitès ki optimize pou pouvwa pou koneksyon seri amelyore, yon modil endpoint PCI Express ki konpatib ak PCI Express, yon MAC Ethernet tri-eta (kontwolè aksè medya), ak yon mikwo-pèfòmans PowerPC 440. modil entegre ki pèmèt konsèpteur lojik avanse yo enkòpore nivo ki pi wo nan pèfòmans nan sistèm ki baze sou FPGA yo.

Fanmi Virtex-6 ofri dènye, karakteristik ki pi avanse nan mache FPGA la.Virtex-6 FPGA yo se fondasyon teknoloji silikon pwogramasyon pou sib tès ki bay konpozan pyès ki nan konpitè ak lojisyèl pou ede konsèpteur yo konsantre sou inovasyon yon fwa efò devlopman yo te inisye.Fanmi Virtex-6 la gen yon achitekti poto ASMBL (modil pòtfolyo silikon avanse) twazyèm jenerasyon ki gen ladan plizyè sousfami diferan.Apèsi sa a dekri aparèy yo nan soufanmi LXT, SXT, ak HXT.Chak sou-fanmi gen yon konbinezon diferan de karakteristik pou satisfè avèk efikasite yon pakèt kondisyon konsepsyon lojik avanse.Anplis twal lojik pèfòmans-wo, Virtex-6 FPGA yo gen ladan plizyè modil nan nivo sistèm entegre.Karakteristik sa yo pèmèt konsèpteur lojik yo bati nivo ki pi wo nan pèfòmans ak fonksyonalite nan sistèm FPGA yo.Virtex-6 FPGA yo tou bay pi bon solisyon pou satisfè bezwen konsèpteur lojik pèfòmans segondè, konsèpteur DSP pèfòmans segondè, ak konsèpteur sistèm entegre pèfòmans segondè, ki pote lojik san parèy, DSP, koneksyon, ak kapasite mikwoprosesè mou.

Virtex-7 se yon pwodwi FPGA ultra-wo fen ki te entwodwi an 2011 sou yon pwosesis 28nm ki bay kliyan libète pou rantre ak debouche karakteristik ki diminye pri ak konsomasyon pouvwa pandan y ap ogmante pèfòmans ak kapasite, kidonk diminye envèstisman devlopman ak deplwaman pou tou de ba. -Pri ak segondè-pèfòmans fanmi yo.Anplis de sa, yon rediksyon pri 35% konpare ak Virtex-6 asire pa gen okenn konvèsyon incrémentielle oswa envestisman jeni, plis ogmante pwodiktivite.

.png)